DVT IDE惊艳!UVM运行时解析,芯片验证狂飙!

芯片作为现代科技的基石,其复杂程度日益提升,功能验证在整个设计流程中占据着举足轻重的地位。如果没有全面而深入的验证,即使是最精妙的设计也可能功亏一篑。在当前的集成电路设计领域,通用验证方法学(UVM)已经成为业界公认的标准,它为验证工程师提供了一套结构化、可重用且高效的验证环境构建框架。然而,UVM环境的动态特性也给传统的EDA(电子设计自动化)工具带来了新的挑战。

新媒网跨境获悉,验证代码与设计代码在性质上有着显著区别。当我们谈及EDA工具如何“解析”(elaboration)代码时,通常指的是工具读取设计或验证代码后,进行一系列的错误检查,并构建一个复杂的内部模型,这个模型能够全面反映代码的各个方面。以我们日常使用的DVT IDE集成开发环境为例,它会对设计代码进行全面的解析。这意味着工具会构建一个包含完整设计层级、所有参数计算、生成模块计算以及绑定等信息的模型。通过这个模型,设计工程师可以便捷地探索设计层级、追踪信号和参数,甚至绘制原理图,从而进行诸多有价值的操作。

然而,对于验证代码的处理则需要更为精细的考量。在基于UVM的验证环境中,EDA工具同样会构建一个完整的模型。验证工程师常常会构建一个与设计层级部分对应的组件树,例如驱动器(drivers)和监视器(monitors),它们被组织在UVM测试平台(testbench)组件中。此外,工程师还会定义并实例化验证专用的组件,如记分板(scoreboards)和序列器(sequencers)。所有这些组件都通过事务级建模(TLM)端口相互连接,共同定义了一个完整的验证拓扑结构。

尽管验证拓扑结构在某些方面与设计层级相似,但其构建方式却有着根本性的不同。设计层级通常是静态定义的,就像一个顶层模块实例化子模块那样,可以在编译时静态地计算出来。然而,UUVM验证组件层级则是在仿真时间点0(time 0)执行特定的UVM流程时动态构建的。在这个执行过程中,所有通过“config db”机制进行的配置设置和获取操作都会完成,所有的工厂覆盖(factory overrides)机制也都会被应用,诸如此类。这就像一个复杂的乐高积木,虽然零件(组件)是预先存在的,但如何组装(拓扑)则是在游戏开始的那一刻才根据一系列规则和指令动态确定的。

这就意味着,在UVM的0阶段(即仿真时间点0的活动)执行完成之前,验证解析是无法彻底完成的。传统的做法可能需要调用一个第三方的仿真器来执行这个过程,但这无疑会增加时间和额外的开销。为了解决这一痛点,DVT IDE采取了一种创新性的方法:它在内部执行一个“run 0”操作,从而使所有的UVM解析得以在IDE内部完成。我们称之为UVM运行时解析(UVM runtime elaboration),以准确反映其动态非静态的特性。

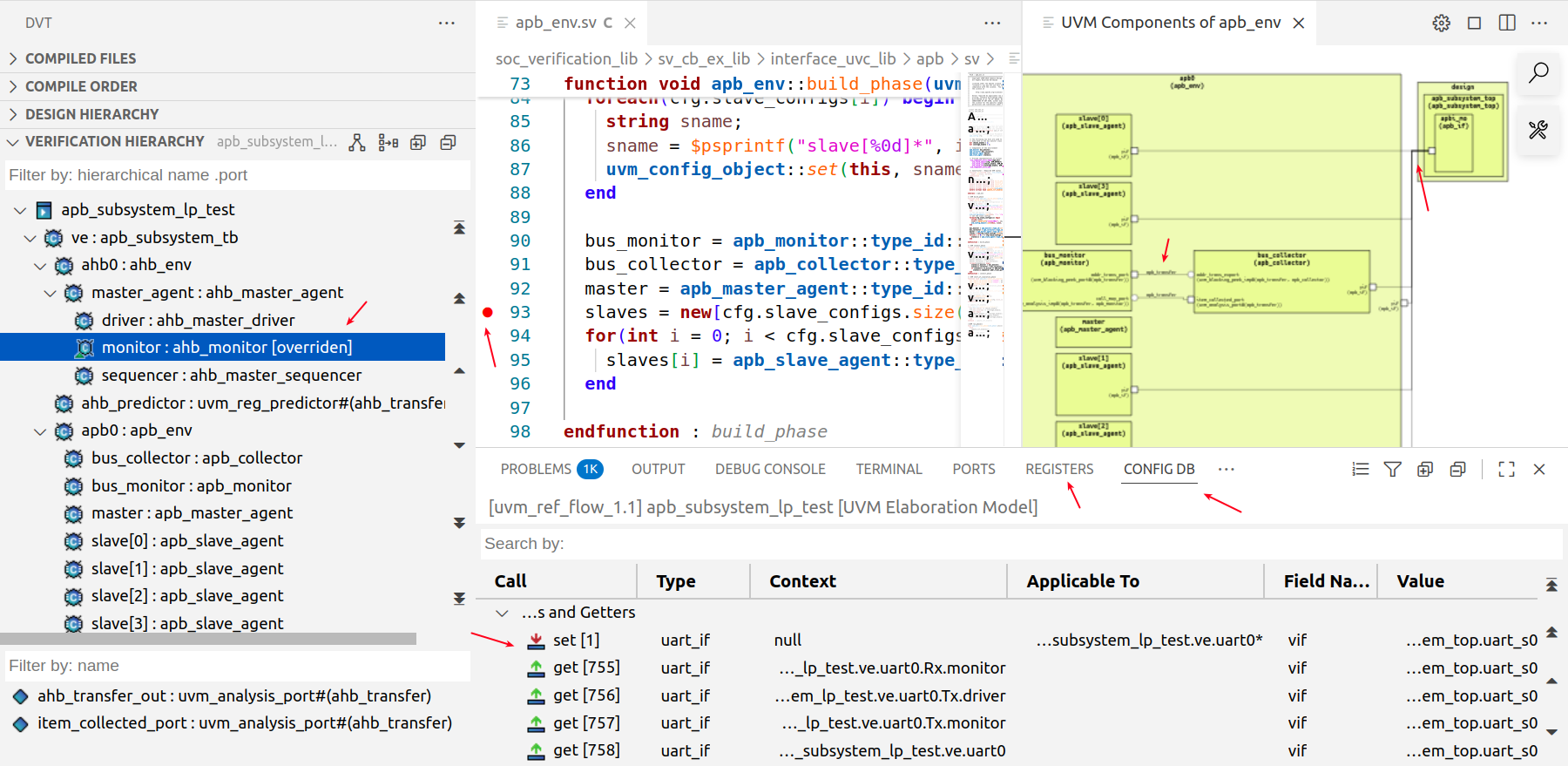

DVT IDE的UVM运行时解析功能为工程师提供了前所未有的便捷。用户可以请求对特定的UVM测试进行运行时解析,并利用断点(breakpoints)来调试“run 0”的执行过程。当断点中断执行时,用户可以浏览每个并行线程上的调用堆栈(call stacks)并检查变量。DVT IDE提供了多种类型的断点,包括条件断点,允许用户根据特定条件暂停执行。工程师可以便捷地查看函数调用堆栈以及在项目中设置的所有断点。此外,他们还可以单步执行代码,检查变量值,添加日志点(log points)来打印信息而无需修改验证代码,甚至可以添加观察点(watchpoints)来在变量值发生变化时中断执行。在UVM运行时解析过程中,DVT IDE会收集大量关键信息,例如:工厂覆盖的定义及其应用位置;配置数据库(config database)的详细信息,包括设置(set)和获取(get)调用的配对情况;寄存器模型(register model)的相关信息,包括地址和位域(bitfield)的计算;物理接口如何连接到虚拟接口的信息;以及TLM端口的连接情况。

所有这些被收集起来的信息都可以在DVT IDE中直观地呈现给工程师,极大地帮助他们探索验证拓扑结构、组件树、寄存器模型以及配置数据库等。DVT IDE甚至能够展示一个嵌套组件的图形化视图,包括它们通过TLM端口进行的连接,以及它们通过虚拟接口与设计之间的连接。这一功能被形象地称为UVM组件图(UVM Components Diagram),它将复杂的验证环境以一目了然的方式呈现在工程师面前,大大提升了理解和调试的效率。

虽然部分验证拓扑可以通过静态分析来确定,但UVM运行时解析的独特之处在于它能够计算出与仿真器在时间点0实际发生的情况完美匹配的真实数据。工程师无需访问外部仿真器就能获得上述所有优势。这极大地节省了时间,因为内部的UVM运行时解析比调用外部工具并构建完整的仿真模型要快得多。这种效率的提升对于芯片研发周期至关重要,意味着能够更快地发现和解决问题,加速产品的上市进程。

新媒网跨境认为,除了上述核心功能之外,UVM运行时解析还提供了其他几个显著的优势,进一步提升了用户体验和工作效率。首先,许多验证环境除了UVM SystemVerilog代码外,还会使用C模型。DVT IDE支持在“run 0”期间进行DPI-C调用,这意味着验证工程师可以无缝地集成C模型,无需担心兼容性问题,这为混合语言验证环境提供了强大的支持。其次,当验证代码发生变化时,用户无需重新经历耗时的编译和设计解析过程。DVT IDE能够增量分析代码变更,并快速执行UVM运行时解析,确保工程师始终能够基于最新的代码进行验证和调试,从而大大缩短了迭代周期。最后,解析完成后,DVT IDE还会保存一个数据库。这意味着如果UVM拓扑结构没有发生变化,验证工程师可以随时加载这个快照,而无需再次执行运行时解析。这对于日常工作中的重复性任务来说,无疑是一个巨大的时间节约。

总而言之,UVM运行时解析是一项成熟且经过实践验证的技术,它通过创新的方式解决了UVM验证环境动态性带来的挑战。这些功能在多年的实践中已经得到了众多用户的广泛认可和验证。这项技术不仅仅是一个工具层面的优化,更是对整个芯片验证流程效率和质量的深刻提升。对于追求卓越的验证工程师而言,深入了解和应用UVM运行时解析无疑将是提升其工作效能的关键。

新媒网跨境预测,随着未来芯片设计复杂度的不断攀升以及验证周期的日益压缩,类似DVT IDE这种能够提供高效UVM运行时解析能力的EDA工具将变得更加不可或缺。它们不仅能帮助工程师更快地定位和解决问题,更能推动整个集成电路产业迈向更高的设计自动化水平。

新媒网(公号: 新媒网跨境发布),是一个专业的跨境电商、游戏、支付、贸易和广告社区平台,为百万跨境人传递最新的海外淘金精准资讯情报。

本文来源:新媒网 https://nmedialink.com/posts/dvt-ide-uvm-elaboration-speeds-chip-verify.html

粤公网安备 44011302004783号

粤公网安备 44011302004783号