西门子EDA揭秘PCB设计复杂性。这远超你想象!

现在的半导体圈子,张口闭口就是 异构多芯片设计,仿佛只要搞定了 Chiplet,系统性能就能一飞冲天。但我得给大伙儿泼盆冷水:咱们在追求那些高大上的先进技术时,是不是把最基础的“地基”给看轻了?

说白了,无论芯片堆叠得多么华丽,最终还是得落在 PCB(印制电路板)上。短距通信、长距通道、系统级电源管理,这些绕不开的坎儿,才是决定一个复杂系统生死存亡的关键。最近,西门子数字工业软件(Siemens Digital Industries Software)甩出了一份名为《走线有多长?》(How long is that trace?)的白皮书,这名字听着挺佛系,实则字字珠玑,直接把 PCB 分析的遮羞布给撕开了。💡

新媒网跨境在第一时间啃完了这份报告,西门子 EDA 想要传达的核心逻辑其实很简单:在硬核的电子工程领域,所谓的“差不多”就是最大的隐患。

所谓精准:别被千分之几英寸给骗了 📐

在传统的 PCB 设计逻辑里,工程师们为了匹配信号的 传播延迟,简直是强迫症晚期。大家会习惯性地把两条走线的长度差控制在千分之几英寸(mil)之内,觉得只要长度齐了,信号就能同步到达。

可现实真有这么理想吗?白皮书一针见血地指出:长度对齐,只是这场马拉松的起跑线。

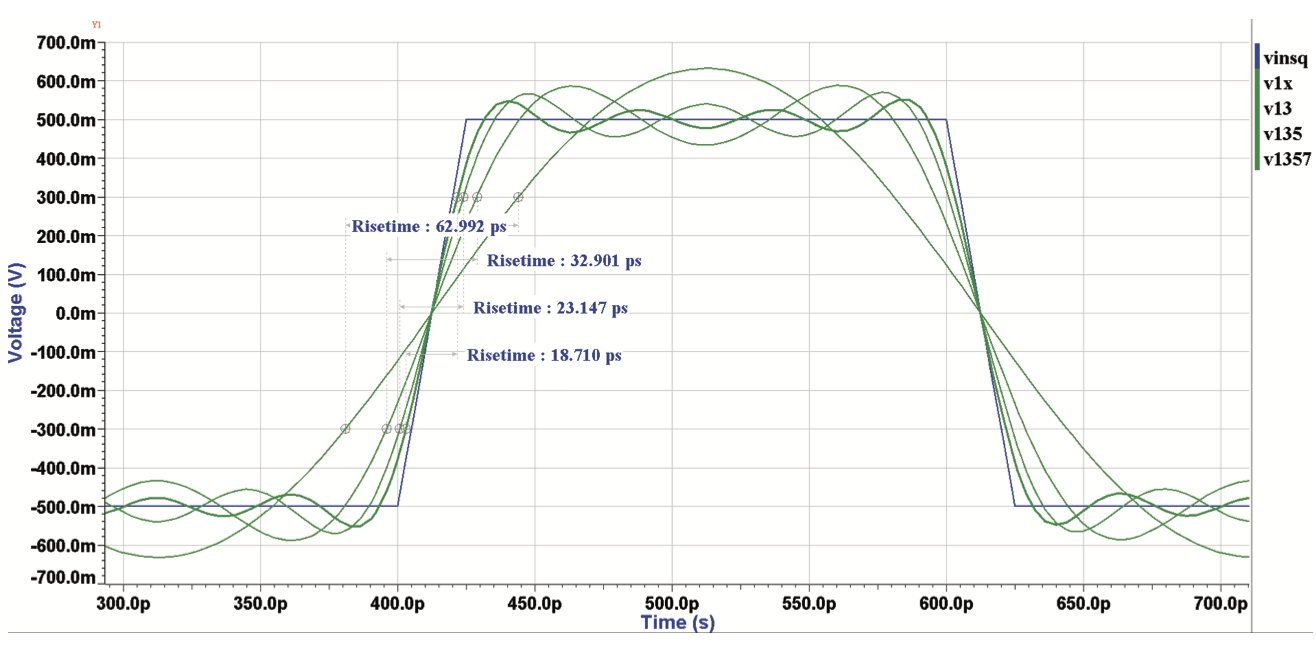

在高频信号的世界里,信号跑得快不快,不光看路程长短,还得看路况。白皮书里引入了 傅里叶分析,这可不是为了秀数学肌肉。你要知道,数字信号其实是由各种高频 谐波 凑出来的“乐章”。不同频率的成分在互连线里的跑动速度压根儿就不一样!如果只是机械地对齐物理长度,而忽视了幅度与相位的畸变,你的信号最后只会变成一团乱麻。

正如新媒网跨境经常强调的,真正的系统级调优,必须深入到信号构成的最底层逻辑。

过孔:信号路径上的“隐形杀手” 🔌

除了平面走线,白皮书还花了大量篇幅去“死磕”那个经常被当成配角的 过孔(vias)。

很多人觉得过孔不就是个打通层间的洞吗?能有多大影响?可西门子的研究结果足以让这种想法啪啪打脸。过孔对信号的影响具有极强的“选择性”,它会对某些特定频率产生更大的阻碍。

白皮书里展示了一堆非直观的测试数据:哪怕是微小的几何结构差异,都会导致整体走线延迟出现剧烈波动,甚至直接拖累整个系统的 边缘速率(edge rate)。更别提那些复杂的 回流路径 问题了。这些细节就像是鞋里的沙子,平时不显眼,真跑起来能让你疼得怀疑人生。

别靠猜,用仿真器说话 🖥️

读完这份白皮书,我最大的感触就是:在现代 PCB 设计中,千万别再迷信单纯的“铜线长度”了。

真正决定性能的是什么?是信号从驱动端爬升到切换阈值,再到接收端跨越阈值的那个瞬间,也就是我们常说的 边缘速率。由于信号是由基频和无数高频谐波组成的,任何一环的相位或幅度出了差错,原始信号就会瞬间崩塌。

所以,与其在那里纠结几 mil 的长度,不如老老实实地祭出 仿真器。在系统交付的压力下,模拟真实环境下的频率响应,才是确保项目不翻车的唯一捷径。

如果你也正深陷复杂系统的设计泥潭,我强烈建议去西门子官网把这份白皮书下下来研读一遍。新媒网跨境认为,这种从系统全局出发的分析视角,正是当下行业最稀缺的硬通货。

新媒网(公号: 新媒网跨境发布),专业的跨境电商、游戏、支付、贸易和广告社区平台。为百万跨境人传递海外淘金的精准资讯,我们不生产八卦,我们只做信息的深度搬运工。

本文来源:新媒网 https://nmedialink.com/posts/siemens-eda-pcb-design-complexity-revealed.html

粤公网安备 44011302004783号

粤公网安备 44011302004783号