跨境2024新突破!Solido套件让高速芯片验证提速。

高速信号技术是现代电子系统发展不可或缺的基石,广泛应用于存储器接口、SerDes通道、数据中心背板以及汽车互联等多个领域。然而,伴随数据传输速率的飙升,信号失真问题日益凸显,例如码间干扰(Inter-Symbol Interference, ISI)、通道损耗以及色散效应等,都对信号完整性构成了严峻挑战。特别是在高带宽存储(High-Bandwidth Memory, HBM)和双倍数据速率(Double Data Rate, DDR)等领域,为了确保信号眼图的有效开合,连续时间线性均衡(Continuous Time Linear Equalization, CTLE)和判决反馈均衡(Decision Feedback Equalization, DFE)等均衡技术已成为关键。

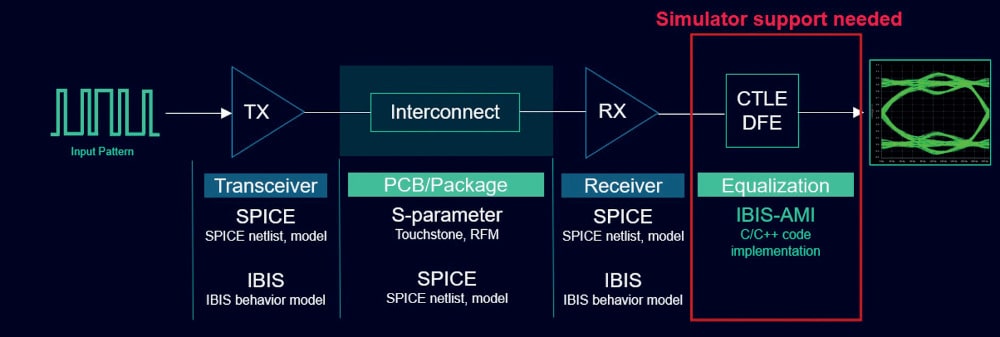

验证这些高速链路的信号完整性,需要兼顾SPICE仿真精度与IBIS及IBIS-AMI模型的应用。对于芯片内部电路或模块级电路,SPICE模型仍是不可或缺的分析工具。在这一背景下,一家领先的科技公司开发出了一款创新工具,能够将IBIS、IBIS-AMI模型、S参数互连模型以及SPICE仿真有机结合,从而实现对高速链路的全面验证。

IBIS-AMI技术解析

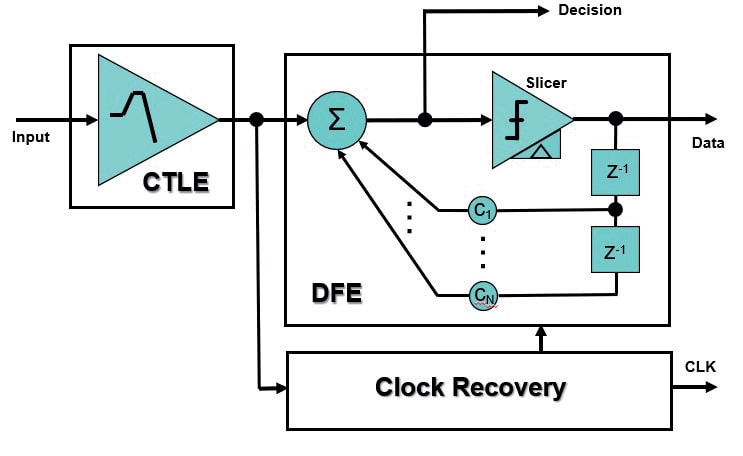

IBIS-AMI(Algorithmic Modeling Interface)是一种描述高速串行接口收发器行为的算法模型接口。通过IBIS-AMI,工程师们能够有效仿真CTLE和DFE等均衡效果,这对于高速通道仿真至关重要。

接收端(Rx)的IBIS-AMI数据流模型包含了其内部各项功能的算法描述,例如CTLE、DFE以及时钟恢复(Clock Recovery)等。这些算法模型使得仿真器能够精确模拟芯片在实际工作状态下的均衡和时钟同步行为。

回顾过往,工程师在进行仿真时,通常需要在一个工具中处理SPICE网表、S参数文件和IBIS模型,再切换到另一个独立的工具处理IBIS-AMI模型,这导致了多次迭代和冗长的验证周期。新媒网跨境获悉,如今,通过集成解决方案,可以在单一仿真环境中对这些电路进行验证,显著减少了迭代次数,并缩短了整体验证时间。

Solido仿真套件

在2024年,这家科技公司对外发布了Solido仿真套件,该套件包含以下核心组件:

- Solido SPICE

- Solido LibSPICE

- Solido FastSPICE

其中,Solido SPICE仿真器支持IBIS-AMI模型、IBIS模型、S参数、损耗耦合传输线模型以及用于高速信号项目的DSPF(Digital Signal Processing Filter)文件。通过Solido SPICE进行验证,能够在通道、I/O缓冲器和电源完整性(Power Delivery)存在的情况下,有效揭示AMI均衡眼图中出现的非线性效应,从而提供更准确的信号完整性分析。

DDR5内存接口验证应用

利用Solido SPICE,工程师能够对芯片间(Chip-to-Chip, C2C)和芯片到模块(Chip-to-Module, C2M)的设计进行验证。在此类应用中,核心芯片可以采用SPICE级别的详细模型,而接收端(Rx)芯片则可以采用IBIS和IBIS-AMI模型进行描述。以DDR5应用为例,C2C的读写周期验证可以通过发送端(Tx)或接收端(Rx)建模为IBIS和IBIS-AMI来实现。数字均衡功能通过IBIS-AMI进行建模,随后Solido SPICE能够对混合了SPICE级别和各种模型的系统进行综合仿真,确保DDR5接口的稳定运行。

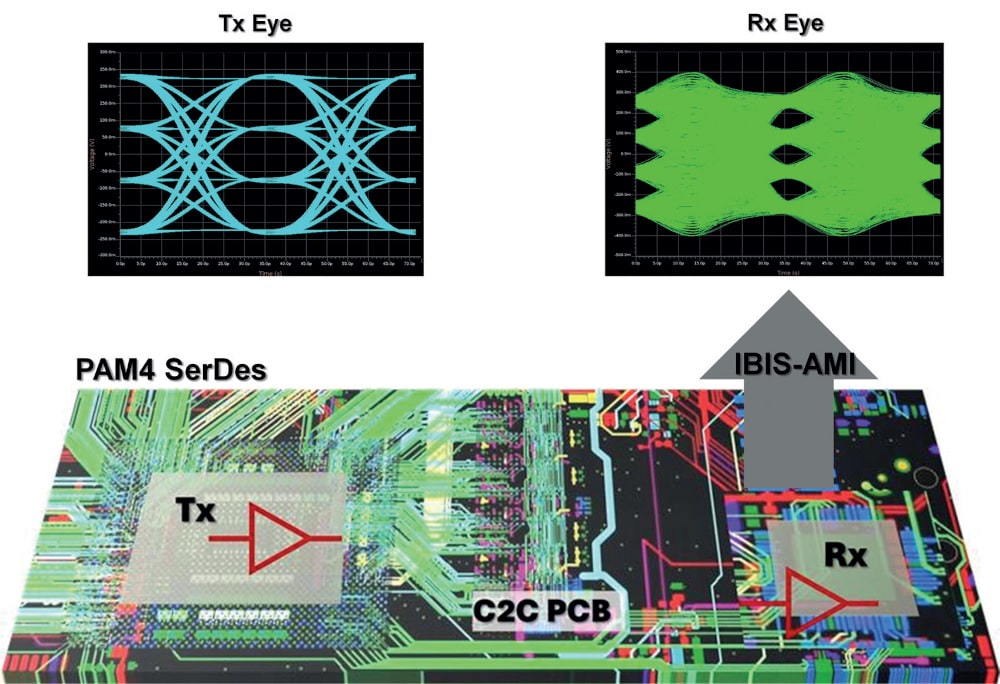

SerDes高速接口验证应用

以下图所示,展示的是一个在28Gbaud PAM4 C2C接口上经过AMI处理后的接收端眼图。在该仿真场景中,发送端(Tx)采用SPICE级别模型进行详细描述,同时包含了PCB互连、介电损耗以及边缘连接器等物理层模型。接收端(Rx)则利用IBIS-AMI模型实现CTLE和DFE均衡功能,以补偿信号在高速传输中的损耗和失真,最终呈现出高质量的信号眼图。

此外,IBIS-AMI模型还支持对不归零码(Non-Return-to-Zero, NRZ)和四电平脉冲幅度调制(Pulse Amplitude Modulation 4, PAM4)的时钟数据恢复(Clock and Data Recovery, CDR)功能进行建模。

Solido SPICE通过整合IBIS和IBIS-AMI模型,实现了对高速DDR5和SerDes芯片设计的SPICE级别验证,这意味着即使是来自不同制造商的芯片,也能在同一个电子系统中进行仿真,极大地提升了系统级验证的灵活性和准确性。

HyperLynx SI的协同效应

通过HyperLynx SI工具,系统设计师即使不是专业的信号完整性(SI)专家,也能在系统和板级层面进行信号完整性分析。Solido SPICE的用户能够共享HyperLynx的IBIS-AMI技术,这确保了在电路级和系统级工具之间切换时,分析结果的一致性。这种技术共享为工程师提供了无缝的工作流程,提升了设计效率。

总结

高速信号传输对验证方法的准确性提出了极高要求。SPICE仿真作为能够捕捉低至晶体管级非线性效应的强大工具,其对IBIS-AMI模型的支持对于SerDes、HBM以及其他采用PAM4编码的应用至关重要。Solido SPICE凭借其强大的功能,能够准确而快速地验证这些复杂的系统。

如需深入了解,可查阅该公司在线发布的《将SPICE与IBIS-AMI结合:使用Solido SPICE解决高级信号完整性验证挑战》白皮书,该白皮书共计10页,提供了详尽的技术解析。

新媒网(公号: 新媒网跨境发布),是一个专业的跨境电商、游戏、支付、贸易和广告社区平台,为百万跨境人传递最新的海外淘金精准资讯情报。

本文来源:新媒网 https://nmedialink.com/posts/cross-border-2024-solido-chip-verify-boost.html

粤公网安备 44011302004783号

粤公网安备 44011302004783号